Bistabilno kolo

U digitalnoj elektronici, bistabilno kolo (leč, flip-flop) je elektronsko kolo koje ima dva stabilna stanja i stoga je u stanju da posluži kao jedan bit memorije. Bistabilno kolo se kontroliše jednim ili dva kontrolna signala i/ili signalom dozvole. Izlaz često pored normalnog ima i komplementni izlaz. Bistabilna kola takođe zahtevaju ulaze za napajanje i masu.

Bistabilna kola mogu biti asinhrona ili sinhrona. Asinhrona bistabilna kola se sastoje od dva ukrštena invertujuća elementa - tranzistora, NI ili NILI kola.[1] Sinhroni flip-flop je verzija asinhronog koji ima dodatni ulaz (C ili CLK, od engleske reči clock - sat, odnosno EN ili ENABLE, od reči enable - dozvoliti) na koji se dovode sinhronizacijski impulsi konstantne frekvencije tako da flip-flop menja stanje na promenu okidnog signala ili signala dozvole. Sinhrona bistabilna kola su specijalno projektovana za sinhrone sisteme i zato ignorišu stanja na svojim ulazima osim u trenutku promene okidnog signala.[2][3] Ovo prouzrokuje da bistabilno kolo može da ili promeni ili da zadrži svoj izlazni signal koji zavisi od vrednosti ulaznih signala za vreme prelaza. Neka bistabilna kola menjaju vrednost izlaza duž celo pozitivnog ili negativnog dela okidnog signala, neki na rastućoj ivici okidnog signala, a drugi na opadajućoj ivici. Bistabilna kola kod kojih izlaz stalno prati promene na ulazima dok se eventualno ne dovede pobudni signal koji zamrzava stanje na izlazu se se nazivaju leč kolima (eng. latch), dok se kola kod kojih se izlaz menja samo posle dovođenja odgovarajuće ivice pobudnog signala nazivaju flip-flopovi. U literaturi i katalozima se često ne pravi razlika između lečeva i flip-flopova, pa se obe vrste kola nazivaju flip-flop. [4] Taktovani flip-flopovi se tipično izrađuju kao master-slejv uređaji, u kom dva osnovna flip-flopa (uz neka dodatna logička kola) sarađuju da ga učine neosetljivim na šumove između prelaza pobudnog signala; ali ipak oni često imaju asinhrone clear i set ulaze koji mogu da promene trenutni izlaz nezavisno od takta.

Flip-flopovi se mogu dalje podeliti u tipove koji mogu imati zajedničku primenljivost i u asinhronim i u taktovanim sekvencijalnim sistemima: SR ("set-reset"), D ("data"), T ("toggle") i JK tipovi su uobičajeni; svi oni se mogu izvesti od (većine) drugih tipova uz nekoliko logičkih kapija. Ponašanje nekog tipa flip-flopa se može opisati karakterističnom jednačinom, koja daje sledeći izlaz u zavisnosti od ulaznih signala i/ili trenutnog izlaza.

Istorija[uredi | uredi izvor]

Prvi elektronski flip-flop su izmislili 1919. Vilijam Ekles i Frenk Vilfred Džordan.[5][6] U početku je nazivan Ekles-Džordanovo okidačko kolo i sastojalo se od dva aktivna elementa (elektronske cevi).[7] Ime flip-flop je kasnije nadenuto po zvuku koji se dobijao na zvučnku proključenom na jedan od spregnutih pojačala tokom procesa okidanja u kolu.

Dizajn je korišćen u britanskom računaru za razbijanje šifri Kolosus iz 1943.[8] i takva kola i njihove tranzistorizovane verzije su bila uobičajena u računarima čak i nakon uvođenja integrisanih kola, iako su zasuni i flip-flopovi napravljeni od logičkih kapija takođe uobičajeni sada.[9][10] Rani zasuni su bili poznati na različite načine kao kola za okidanje ili multivibratori.

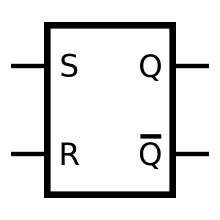

SR flip-flop[uredi | uredi izvor]

SR flip-flop ima dva ulaza S i R po kojima je i dobio ime. Ulaz S se naziva setujući ulaz (eng. set - postaviti), dok je ulaz R resetujući ulaz (eng. reset - poništiti).

Postavljanjem ulaza S u logičko stanje 1, a ulaza R u logičko stanje 0 izlaz Q se postavlja u stanje 1, a izlaz Q' u stanje 0. Ukoliko se na ulaz S dovede logička 0, a na ulaz R logička 1 na izlazu Q se dobije logička 0, a na izlazu logička 1.

Ako se na ulaze S i R istovremeno dovede logička 0, na izlazu se ne dešava nikakva promena, dok se istovremenim dovođenjem logičke 1 uzrokuje nepredviđeno stanje na izlazu, pa se ova kombinacija naziva zabranjeno stanje.

Najčešći način zapisivanja rada flip-flopa je korišćenjem tabele stanja:

| SR flip-flop (izrađeno pomoću EKSILI kola) | ||||||||

|---|---|---|---|---|---|---|---|---|

| Funkcionalna tabela |

Eksitaciona tabela | |||||||

| S | R | Qn+1 | Q | Qn+1 | S | R | Komentar | |

| 0 | 0 | zadržava stanje | 0 | 0 | 0 | X | nema promene | |

| 0 | 1 | Q = 0 | 1 | 0 | 0 | 1 | reset | |

| 1 | 0 | Q = 1 | 0 | 1 | 1 | 0 | set | |

| 1 | 1 | nestabilna kombinacija | 1 | 1 | X | 0 | nedozvoljeno stanje | |

| Napomena: Znak „X“ označava da je signal proizvoljan za datu kombinaciju na ulazu. | ||||||||

Iz ove tablice se direktno dobija jednačina:

i uz činjenicu da je za dozvoljena stanja na ulazu SR=0, dobija se prostija jednačina:

JK flip-flop[uredi | uredi izvor]

JK flip-flop nadograđuje rad SR flip-flopa tretiranjem stanja S = R = 1 kao naredbu za „obrtanje“. Kombinacija J = 1, K = 0 je komanda da se setuje flip-flop; kombinacija J = 0, K = 1 je komanda da se resetuje flip-flop; a kombinacija J = K = 1 menja izlaz u logički komplement svoje trenutne vrednosti. Kada je J = K = 0, izlazi flip-flopa će zadržati svoje prethodno stanje.

Tabela stanja flip-flopa je:

| JK flip-flop | ||||||||

|---|---|---|---|---|---|---|---|---|

| Funkcionalna tabela |

Eksitaciona tabela | |||||||

| J | K | Qn+1 | Komentar | Q | Qn+1 | J | K | Komentar |

| 0 | 0 | Q | na čekanju | 0 | 0 | 0 | X | nema promene |

| 0 | 1 | 0 | reset | 0 | 1 | 1 | X | set |

| 1 | 0 | 1 | set | 1 | 0 | X | 1 | reset |

| 1 | 1 | Q | promena | 1 | 1 | X | 0 | nema promene |

Karaktetistična jednačina JK flip-flopa je:

Promena stanja JK flip-flopa se zbog prisustva I kola može vršiti samo kada je okidni impuls aktivan na visokom nivou. Kako stanja na izlazu menja i stanje na ulazu logičkih kola, tako da se resetovani flip-flop može ponovo setovati ako je okidni signal još uvek aktivan. Kolo sa slike desno će ispravno raditi samo ako je okidni signal vrlo kratak, odnosno kraći od kašnjenja kroz logička kola i SR leč kolo. Kako su vremenska kašnjenja odložna velikim varijacijama usled proizvodnih tolerancija i promena ambijenta, rad ovakvog flip-flopa može biti nepouzdan. Stoga se JK flip-flopovi uvek realizuju pomoću složenijih konfiguracija sa master-slejv ili ivičnim okidanjem.

T flip-flop[uredi | uredi izvor]

T flip-flop ima jedan ulaz T (od reči toggle - prekidač ili trigger - okidač). Ovaj flip-flop okida samo kada je na ulazu visok signal, i onda menja stanje izlaza u komplement sadašnjeg stanja.

Karakteristična jednačina T flip-flopa je:

- (ili, bez upotrebe EKSILI vrata, ekvivalent je: ),

a može biti opisana pomoću sledeće tabele:

| T flip-flop | ||||||||

|---|---|---|---|---|---|---|---|---|

| Funkcionalna tabela |

Eksitaciona tabela | |||||||

| Komentar | Komentar | |||||||

| 0 | 0 | 0 | zadržava stanje | 0 | 0 | 0 | nema promene | |

| 0 | 1 | 1 | zadržava stanje | 1 | 1 | 0 | nema promene | |

| 1 | 0 | 1 | prekida | 0 | 1 | 1 | komplement | |

| 1 | 1 | 0 | prekida | 1 | 0 | 1 | komplement | |

Pošto vrši promenu stanja na izlazu pri svakom dovedenom visokom nivou na ulaz, T flip-flop faktički deli broj ulaznih impulsa sa dva, tj, ako je frekvencija okidačkog signala 4 MHz, izlazna frekvencija dobijena iz T flip-flopa biće 2 MHz. Ova „podjeljiva“ opcija ima upotrebu u raznim digitalnim brojačima.

T flip-flop se može realizovati pomoću JK flip-flopa (J i K ulazi su zajedno spojeni i ponašaju se kao T ulaz) ili pomoću D flip-flopa (T ulaz i Qn su povezani na D ulaz pomoću EKSILI vrata).

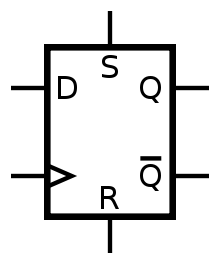

D flip-flop[uredi | uredi izvor]

D flip-flop je trenutno najkorišćeniji flip-flop u digitalnoj elektronici. Najčešće se koristi u stacionarnim registrima i memorijskim modulima. Izlaz Q preuzima stanje na ulazu D (od engleske reči Delay - kašnjenje, zbog zadržavanja ulaza za jedan taktni interval) u trenutku kada je taktni signal na aktivnoj ivici. Tabela stanja za D flip-flop:

| Takt | D | Qn+1 | Qn+1 |

|---|---|---|---|

| rastuća ivica | 0 | 0 | 1 |

| rastuća ivica | 1 | 1 | 0 |

| opadajuća ivica | X | Q | Q |

Generalizacije[uredi | uredi izvor]

Flip-flopovi se mogu generalizovati na najmanje dva načina: tako što će biti 1-od-N umesto 1-od-2, i prilagođavanjem logici sa više od dva stanja. U posebnim slučajevima kodiranja 1 od 3, ili viševrednosne ternarne logike, takav element se može nazvati flip-flap-flop.[11]

U konvencionalnom flip-flopu, tačno jedan od dva komplementarna izlaza je visok. Ovo se može generalizovati na memorijski element sa N izlaza, od kojih je tačno jedan visok (alternativno, gde je tačno jedan od N nizak). Izlaz je stoga uvek jedno-vruća (odnosno jedno-hladna) reprezentacija. Konstrukcija je slična konvencionalnom unakrsno spojenom flip-flopu; svaki izlaz, kada je visok, inhibira sve ostale izlaze.[12] Alternativno, mogu se koristiti manje ili više konvencionalni flip-flopovi, jedan po izlazu, sa dodatnim kolom kako bi se osiguralo da samo jedan po jedan može biti istinit.[13]

Još jedna generalizacija konvencionalnog flip-flopa je memorijski element za viševrednosnu logiku. U ovom slučaju memorijski element zadržava tačno jedno od logičkih stanja sve dok kontrolni ulazi ne izazovu promenu.[14] Pored toga, može se koristiti i sat sa više vrednosti, što dovodi do novih mogućih prelaza takta.[15]

Reference[uredi | uredi izvor]

- ^ For example, Digital Equipment Corporation's Logic Handfbook Flip Chip™ Modules 1969 edition calls transparent RS latches as "R/S Flip Flops" (http://www.bitsavers.org/pdf/dec/handbooks/Digital_Logic_Handbook_1969.pdf page 44)

- ^ Pedroni, Volnei A. (2008). Digital electronics and design with VHDL. Morgan Kaufmann. str. 329. ISBN 978-0-12-374270-4.

- ^ Latches and Flip Flops Arhivirano na sajtu Wayback Machine (5. oktobar 2016) (EE 42/100 Lecture 24 from Berkeley) "...Sometimes the terms flip-flop and latch are used interchangeably..."

- ^ Roth, Charles H. Jr. (1995). „Latches and Flip-Flops”. Fundamentals of Logic Design (4th izd.). PWS. ISBN 9780534954727.

- ^ GB 148582, Eccles, William Henry & Jordan, Frank Wilfred, "Improvements in ionic relays", published 1920-08-05

- ^ See:

- Eccles, W.H.; Jordan, F.W. (19. 9. 1919). „A trigger relay utilizing three-electrode thermionic vacuum tubes”. The Electrician. 83: 298.

- Reprinted in: Eccles, W.H.; Jordan, F.W. (decembar 1919). „A trigger relay utilizing three-electrode thermionic vacuum tubes”. The Radio Review. 1 (3): 143—6.

- Summary in: Eccles, W.H.; Jordan, F.W. (1919). „A trigger relay utilising three electrode thermionic vacuum tubes”. Report of the Eighty-seventh Meeting of the British Association for the Advancement of Science: Bournemouth: 1919, September 9–13. str. 271—2.

- ^ Pugh, Emerson W.; Johnson, Lyle R.; Palmer, John H. (1991). IBM's 360 and early 370 systems

. MIT Press. str. 10. ISBN 978-0-262-16123-7.

. MIT Press. str. 10. ISBN 978-0-262-16123-7.

- ^ Flowers, Thomas H. (1983), „The Design of Colossus”, Annals of the History of Computing, 5 (3): 249, S2CID 39816473, doi:10.1109/MAHC.1983.10079

- ^ Gates, Earl D. (2000). Introduction to electronics (4th izd.). Delmar Thomson (Cengage) Learning. str. 299. ISBN 978-0-7668-1698-5.

- ^ Fogiel, Max; Gu, You-Liang (1998). The Electronics problem solver, Volume 1 (revised izd.). Research & Education Assoc. str. 1223. ISBN 978-0-87891-543-9.

- ^ Often attributed to Don Knuth (1969) (see Midhat J. Gazalé (2000). Number: from Ahmes to Cantor. Princeton University Press. str. 57. ISBN 978-0-691-00515-7.), the term flip-flap-flop actually appeared much earlier in the computing literature, for example, Bowdon, Edward K. (1960). The design and application of a "flip-flap-flop" using tunnel diodes (Master's thesis). University of North Dakota., and in Alexander, W. (februar 1964). „The ternary computer”. Electronics and Power. IET. 10 (2): 36—39. doi:10.1049/ep.1964.0037.

- ^ „Ternary "flip-flap-flop"”. Arhivirano iz originala 2009-01-05. g. Pristupljeno 2009-10-17.

- ^ US 6975152, Lapidus, Peter D., "Flip flop supporting glitchless operation on a one-hot bus and method", published 2005-12-13, assigned to Advanced Micro Devices Inc.

- ^ Irving, Thurman A.; Shiva, Sajjan G.; Nagle, H. Troy (mart 1976). „Flip-Flops for Multiple-Valued Logic”. IEEE Transactions on Computers. C—25 (3): 237—246. S2CID 34323423. doi:10.1109/TC.1976.5009250.

- ^ Wu, Haomin; Zhuang Nan (jul 1991). „Research into ternary edge-triggered JKL flip-flop”. Journal of Electronics (China). 8 (3): 268—275. S2CID 61275953. doi:10.1007/BF02778378.

Literatura[uredi | uredi izvor]

- Thomas J. Chaney and Charles E. Molnar (april 1973). „Anomalous Behavior of Synchronizer and Arbiter Circuits” (PDF). IEEE Transactions on Computers. C—22 (4): 421—422. ISSN 0018-9340. S2CID 12594672. doi:10.1109/T-C.1973.223730.

- Chaney, Thomas J. „My Work on All Things Metastable OR Me and My Glitch” (PDF). Arhivirano iz originala (PDF) 8. 12. 2015. g. Pristupljeno 5. 11. 2015.

- John Bainbridge (2002). Asynchronous system-on-chip interconnect. Springer. str. 18. ISBN 978-1-85233-598-4.

- Richard F. Tinder (2009). Asynchronous sequential machine design and analysis: a comprehensive development of the design and analysis of clock-independent state machines and systems. Morgan & Claypool Publishers. str. 165. ISBN 978-1-59829-689-1.

- Kleeman, L.; Cantoni, A. „Metastable Behavior in Digital Systems" December 1987”. IEEE Design & Test of Computers. 4 (6): 4—19. S2CID 1895434. doi:10.1109/MDT.1987.295189.

- Harris, Sarah; Harris, David (2015). Digital Design and Computer Architecture: ARM Edition. Morgan Kaufmann. str. 151—153. ISBN 978-0128009116.

- Ginosar, Ran (2011). „Metastability and Synchronizers: A tutorial” (PDF). VLSI Systems Research Center. Electrical Engineering and Computer Science Dept., Technion—Israel Institute of Technology, Haifa. Arhivirano iz originala (PDF) 23. 11. 2018. g. Pristupljeno 27. 06. 2023.

- Xanthopoulos, Thucydides (2009). Clocking in Modern VLSI Systems. Springer Science and Business Media. str. 196. ISBN 978-1441902610.

- „A Metastability Primer” (PDF). Application Note AN-219. Phillips Semiconductor. 1989. Arhivirano iz originala (PDF) 10. 01. 2017. g. Pristupljeno 20. 1. 2017.

- Arora, Mohit (2011). The Art of Hardware Architecture: Design Methods and Techniques for Digital Circuits. Springer Science and Business Media. ISBN 978-1461403975.

Spoljašnje veze[uredi | uredi izvor]

- Another summary of flip-flop types

- Explanation of How Flip Flops Work with Logic Gate Diagrams

- Flip-flops interactive (requires Java)

- FlipFlop Hierarchy Arhivirano 2015-04-08 na sajtu Wayback Machine, shows interactive flipflop circuits.

- The J-K Flip-Flop

- Shirriff, Ken (avgust 2022). „Reverse-engineering a 1960s hybrid flip flop module with X-ray CT scans”.