Динамички RAM

| Типови рачунарске меморије |

|---|

| Променљива |

| RAM |

| У развоју |

| Историја |

|

| Непроменљива |

| ROM |

| NVRAM |

| Раније фазе NVRAM |

| Механичка |

| У развоју |

| Историја |

|

Динамички RAM (енгл. dynamic RAM (dynamic random-access memory — „динамичка меморија са случајним приступом“)) или скраћено DRAM, је тип RAM меморије која чува сваки бит података у посебном кондензатору у оквиру интегрисаног кола. Кондензатор може бити пун или празан; ова два стања представљају две вредности бита, уобичајено се зову 0 и 1. Пошто кондензаторима цури набој, информација би на крају нестала ако се не би кондензатор периодично освежавао. Због ових захтева за освежавање, динамичка меморија је супротна у односу на SRAM и друге статичке меморије.

Главна меморија („RAM“) у личним рачунарима је динамички RAM (DRAM). То је RAM у стоним рачунарима, лаптоповима и радним станицама рачунара, као и неким RAM конзолама за видео игре.

Предност DRAM-а је њогова једноставна структура: само један транзистор и један кондензатор су потребни по биту, у поређењу са 4 или 6 транзистора у SRAM-у. Ово омогућава DRAM-у да постигне велику густину. За разлику од флеш меморија, DRAM је променљива меморија (наспрам непроменљиве меморије), пошто губи податке брзо након престанка напајања. Транзистори и кондензатори који се користе су веома мали; билиони могу да стану на један меморијски чип.

Историја[уреди | уреди извор]

Криптоаланитичка машина под кодним називом Aquarius („Водолија“) коришћена је у Bletchley Park за време Друго светско рата са уграђеном чврсто-жичаном динамичком меморијом. Папир трака је прочитана и знакови на њој „су запамћени у динамичком складишту ... Складиште користи велику банку кондензатора, који су напуњени или не, напуњени кондензатор представља крст (1) а празни кондензатор тачку (0). Пошто напуњени кондензатори постепено цуре, периодични пулс се примењује да напуни оне који су још увек пуни (отуда термин „динамички“)“.[1]

Године 1960. Арнолд Фарбер и Јуџин Шлиг, радећи за IBM, створили су чврсто-ожичену меморијску ћелију, коришћењем транзистор капија и тунел диоду леча (у електроници то је коло које се користи за складиштење информација). Заменили су леч са два транзистора и два отпорника, а конфигурација је постала позната као Farber-Schlig ћелија. Године 1965. Benjamin Agusta и његов тим са IBM-а сворио је 16-битни силиконски меморијски чип заснован на Farber-Schlig ћелији, са 80 транзистора, 64 отпорника, и четири диоде. Године 1966. DRAM је измислио др Robert Dennard у IBM Thomas J. Watson Research Center. Њему је одобрен U.S. патент број 3,387,286 Архивирано на сајту Wayback Machine (31. децембар 2015) 1968. године. Кондензатори су били коришћени за раније меморијске шеме попут бубња од Атанасов-Беријевог рачунара, the Williams-ове цеви и Selectron цеви.

Toshiba "Toscal" BC-1411 електронски калкулатор, који је представљен у невембру 1966. године,[2] користио је облик динамичког RAM-а изграђеног од дискретних компоненти.[3]

Године 1969. Honeywell је затражио од Интела да направи DRAM помоћу 3-транзисторске ћелије које су они развили. Intel их је направио под називом Intel 1102 (1024x1) почетком 1970. године. Међутим, 1102 је имао много проблема, што је навело Intel да започне рад на сопственом побољшаном дизајну, у тајности да би се избегао сукоб са Honeywell. Ово је постало прва комерцијално доступна DRAM меморија, Intel 1103 (1024x1), у октобру 1970. године, упркос почетним проблемима са ниским приносом до пете ревизије масака. 1103 је дизајнирао Joel Karp и изложила Barbara Maness.

Први DRAM са вишеструким редовима и колонама адресних линија био је Mostek MK4096 (4096x1) дизајниран од стране Robert Proebsting и представљен 1973. године. Шеме адресирања користе исте адресне пинове да прими нижу половину и вишу половину адресе меморијске ћелије, која ће се пребацивати између две половине на незменичне циклусе магистрале. Ово је био радикалан напредак, ефективно је преполовио број потребних адресних линија, што је омогућило да стане у пакет са мање пинова, и предност трошкова који су расли са сваким повећањем величине моморије. MK4096 се показао као веома робустан дизајн за корисничке апликације. На густини од 16К, предност трошкова се повећавала; Mostek MK4116 16K DRAM, уведен 1976. године, остварио је више од 75% удела светског DRAM тржишта. Међутим, кад је густина порасла на 65К у раним 90-им годинама, Mostek-а је претекао јапански произвођач DRAM-а, продајући квалитетнији DRAM који користи исту шему мултиплексирања по нижој цени трошкова. Види–United States relations# Frictions у индустријском сектору полупроводника.

Принцип рада[уреди | уреди извор]

DRAM се обично распоређује у правоугаони низ набојних ћелија за складиштење које се састоје од једног кондензатора и транзистора по биту податка. Слика са десне стране приказује једноставан пример 4х4 матричне ћелије. Модерна DRAM матрица су више хиљада ћелија у висину и ширину.

Дуге хиризонталне линије које повезују сваки ред познате су као реч линије. Свака колона ћелија се састоји од две бит-линије, свака повезана са сваком другом ћелијом за складиштење у колони (илустрација са десне стране не укључује овај важан детаљ). Оне су опште познате као + и – бит-линије.

Операције читања бита података са DRAM складишне ћелије[уреди | уреди извор]

- Sense amplifier је искључен. (У модерној меморији рачунара, sense amplifier је један од елемената који чине кола на полупроводничком меморијском чипу (интегрисано коло)).

- Бит-линије су напуњене до тачно једнаких напона који су између високих и ниских логичких нивоа (нап. 0.5V ако су два нивоа 0 и 1V). Бит-линије су физички симетричне да би задржале једнаку капацитивност, па стога у том тренутку њихови напони су једнаки.

- Претходног наелектрисања кола се искључују. Зато што су бит-линије релативно дугачке, оне имају довољно капацитивности да одрже напон кратко време. Ово је пример динамичке логике.

- Жељени редна реч-линија је тада прешла на висок ниво да се повеже са ћелијом капацитатора за складиштење са својом бит-линијом. Ово изазива да транзистор проводи, преноси наелектрисање из складишне ћелије до повезане бит-линије (ако је ускладиштена вредност 1) или од повезане бит-линије ди складишне ћелије (ако је ускладиштена вредност 0). Пошто је капацитивност бит-линије много већа од капацитивност ћелије за складиштење, напон на бит-линији се врло мало повећава ако је кондензатор ћелије за складиште празан и мало се смањује уколико је кондензатор ћелије за складиштење напуњен (нпр. 0.54V и 0.45V у два случаја). Пошто друге бит-линије одржавају 0.50 V постоји мала разлика напона између две уврнуте бит-линије.

- Sense amplifier је да су сада повезани са паровима бит-линија. Позитивни повратак настаје између унакрсно повезаних инвертора, на тај начин се појачава разлика напона између парних и непарних редова бит-линија одређене колоне све док једна бит-линија не буде у потпуности на најнижем нивоу, а друга на максимално високом напону. Када се то деси, ред је „отворен“ (подаци жељене ћелије су на располагању).

- Све ћелије за складиштење на отвореном реду су истовремено осетљиве, и sense amplifier излази лечован. Колона адресе онда бира који леч бит да повеже на екстерну магистралу података. Читање из различитих колона у истом реду може да се изврши без одлагања отварања реда, зато што су за отворени ред, сви подаци већ били осетљиви и лечовани.

- Док се дешава читање колоне у отвореном реду, струја тече уназад на бит-линијама из излаза sense amplifier-а и поново пуни ћелије за складиштење. Ово појачава (тј. „освежава") пуњење у ћелији за складиштење повећањем напона у кондензатору за складиштење ако је био на почетку напуњен, или га држи ненапуњеним ако је био празан. Треба имати на уму да, због дужине бит-линија, постоји прилично дуго ширење кашњења пуњења да буде пребачено натраг на ћелију кондензатора. Ово тражи значајно време за sense amplifier, и тако се преклапа са једном или више колона за читање.

- Када заврши са читањем свих колона у текућем отвореном реду, реч-линија се искључује дисконекцијом ћелија кондензатора за складиштење (ред „затворен") са бит-линије. Sense amplifier је искључен, а бит-линије се поново пуне.

За писање у меморију[уреди | уреди извор]

За складиштење података, ред је отворен и дата колонско осећање појачавача, је привремено приморано да захтева високо или ниско напонско стање, узрокујући да бит-линија пуни или празни ћелију кондензатора за складиштење до жељене вредности. Због осетљивог појачивача позитивна повратна конфигурација, ће одржати бит-линију на стабилном напону и после престанка напона. Током писања на одређену ћелију, све колоне у реду су истовремено осетљиве само током читања, тако да икао једна складишна ћелија капацитатора мења стање, цео ред се освежава (написан поново), као што је проказано на слици десно.

Брзина освежавања[уреди | уреди извор]

Типично, произвођач прецизира да сваки ред мора имати своје ћелије кондензатора за складиштење освежене сваких 65ms или мање, као што је дефинисао JEDEC (Foundation for developing Semiconductor Standards) стандард. Логика освежења је обезбеђена у DRAM контролеру који аутоматизује периодично освежавање, то јест то не морају да извршавају софтвер или други хардвер. Ово чини логику кола контролера компликованом, али та мана је оправдана чињеницом да је DRAM много јефтинији по ћелији за складиштење и пошто је свака ћелија за складиштење једноставна, DRAM има много већи капацитет по јединици површине него SRAM.

Неки системи освежавају сваки ред у рафалу активности које укључују све редове сваких 64ms. Други системи освежавају један ред у тренутку који се распореди у интервалу од 64ms. На пример, систем са 213 = 8192 редова би захтевао распоређено освежавање једног реда сваких 7.5µs што је 64ms подељено на 8192 редова. Неколико система у реалном времену освежава део меморије у времену које је одређено помоћу спољне тајмер функције која регулише рад остатка система, као што је вертикална празнина која се јавља сваких 10-20ms у видео опреми. Све методе захтевају неку врсту бројача да прати који следећи ред треба да се освежи. Већина DRAM чипова укључује бројач. Старији типови су захтевали екстерну логику освежавања за држање бројача.

Под одређеним условима, већина података у DRAM-у може се повратити чак и ако DRAM није био освежен неколико минута.

Тајминг меморије[уреди | уреди извор]

Многи параметри су потребни да се у потпуности опише тајминг DRAM операција. Ево неких примера за два временска разреда синхроног DRAM-а, са листе са подацима објављеним 1998. године:[4]

| "50 ns" | "60 ns" | Опис | |

|---|---|---|---|

| tRC | 84 ns | 104 ns | Насумично време циклуса читања и писања (од једног пуног/RAS цилуса до другог) |

| tRAC | 50 ns | 60 ns | Време приступа: /RAS низак до изван валидних података |

| tRCD | 11 ns | 14 ns | /RAS низак у /CAS ниско време |

| tRAS | 50 ns | 60 ns | /RAS пулсирајућа ширина (минималан/RAS ниско време) |

| tRP | 30 ns | 40 ns | /RAS време претходног пуњења (минималан/RAS високо време) |

| tPC | 20 ns | 25 ns | Циклус времена страна-режим читати или писати (/CAS до /CAS) |

| tAA | 25 ns | 30 ns | Време приступа: Валидне адресе колона до валидних података ван (укључује адресно подешавање времена пре / CAS низак) |

| tCAC | 13 ns | 15 ns | Време приступа: / CAS ниско до валидних података ван |

| tCAS | 8 ns | 10 ns | /CAS ниска пулсирајућа ширина минимална |

Дакле, генерално цитирано број је /RAS време приступа. Ово је време које је потребно да се прочита насумични бит из претходно напуњеног DRAM низа. Време да се прочита додатни бит из отворене странице је много мањи.

Када такав RAM приступи логици генератора такта, времена се генерално заокружују у најближем циклусу. На пример, када се приступа од стране машине са 100 MHz (нпр. 10ns циклу), 50ns DRAM може да изврши прво читање у пет циклуса генаратора такта, а додатно читање у овиру исте стране на свака два циклуса генератора такта. Ово се обично описује као "5-2-2-2" тајминг, као рафал од четири читања унутар стране које су уобичајене.

Кад се описује синхрона меморија, тајминг је описан као циклус генератора такта одвојен цртицом. Ови бројеви представљају tCL‐tRCD‐tRP‐tRAS као умножак DRAM времена циклуса генератора такта. Треба имати на уму да је ово половина брзине податка преноса када се користи двострука брзина преноса података. JEDEC стандард PC3200 тајминг је 3‐4‐4‐8[5] са 200 MHz генератором такта, док премијум цена високох перформаси PC3200 DDR DRAM DIMM може да ради на 2‐2‐2‐5 тајмингу.[6]

| PC-3200 (DDR-400) | PC2-6400 (DDR2-800) | PC3-12800 (DDR3-1600) | Опис | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Обично | Брзина | Обично | Брзина | Обично | Брзина | ||||||||

| такт | време | такт | време | такт | време | такт | време | такт | време | такт | време | ||

| tCL | 3 | 15 ns | 2 | 10 ns | 5 | 12.5 ns | 4 | 10 ns | 9 | 11.25 ns | 8 | 10 ns | /CAS низак на валидном излазу (еквивалентно tCAC) |

| tRCD | 4 | 20 ns | 2 | 10 ns | 5 | 12.5 ns | 4 | 10 ns | 9 | 11.25 ns | 8 | 10 ns | /RAS низак на /CAS ниско време |

| tRP | 4 | 20 ns | 2 | 10 ns | 5 | 12.5 ns | 4 | 10 ns | 9 | 11.25 ns | 8 | 10 ns | /RAS precharge време (минимални precharge за активно време) |

| tRAS | 8 | 40 ns | 5 | 25 ns | 16 | 40 ns | 12 | 30 ns | 27 | 33.75 ns | 24 | 30 ns | Row active time (минимално активно за precharge време) |

Побољшање у односу на 11 година није толико значајно. Минимално насумично време приступа је побољшано од tRAC = 50 ns to tRCD + tCL = 22.5 ns, па чак и премија 20 ns подврста је само 2,5 пута боља у односу на типичан случај (~ 2,22 пута боља). CAS кашњење је још мање побољшано, од tCAC = 13 ns 10 ns. Међутим, DDR3 меморија не постиже 32 пута већи пропусни опсег; због унутрашњег pipelining-а и широких стаза података, она може да има две излазне речи свака 1.25 ns (1600 Mword/s), док EDO DRAM може да има једну излазну реч по tPC = 20 ns (50 Mword/s).

Timing скраћенице[уреди | уреди извор]

|

|

Детекција и корекција грешака[уреди | уреди извор]

Електрична или магнетна интерференција унутар рачунарског система може да изазове да један бит у DRAM-у спонтано промени стање. Већина једнократних ("меких") грешака у DRAM чиповима се јавља као последица радијације, углавном неутрона из космичких зрака секундарно, који може да мења садржај једне или више меморијских ћелија или да омета кола која се користе за њихово читање/писање. Недавна студија[7] је показала да један догађај везан за космичку радијацију драматично опада са геометријом процеса и претходна забринутост над повећањем брзине грешака ћелије су неосноване.

Овај проблем може се ублажити коришћењем вишка меморијских битова и меморијских контролера који користе ове битове, обично имплементираних унутар DRAM модула. Ови додатни битови се користе да запамте парност и да омогуће да се изгубљени подаци реконструишу помоћу кода за изправљање грешака (ECC). Парност омогућава откривање свих једно-битних грешака (у ствари, било који непаран број погрешних бита). Најчешћи код за исправљање грешака је SECDED Хамингов код, омогућава да грешка једног бита буде исправљена и, у уобичајеној конфигурацији, са додатним битом парности, да се детектује грешка два бита.

ECC способан меморијски контролер који се корсти у многим савременим рачунарима обично може да детектује и исправи грешку једног бита у 64-битној речи (јединица преноса магистрале), и да детектује (али не и исправи) грешку два бита у 64-битној речи. Неки системи такође „рибаре“ грешке, писањем исправљене верзије назад у меморију. BIOS у неким рачунарима и оперативним системима као што је Linux, омогућава бројање детектованих и исправљених меморијских грешака; што омогућава идентификацију и замену пропалих меморијских модула.

Недавне студије дају широку варијацију стопе грешака преко седам редова величине разлике, у распону од 10−10−10−17 error/bit·h, отприлије једна грешка бита, по сату, по гигабајту меморије у једној битној грешки, по веку, по гигабајту меморије.[7][8][9] Schroeder 2009 студија пријавила 32% шанси да ће рачунар у својој студији патити од најмање једне исправљиве грешке годишње, а прижио доказе да већина оваквих грешака су испрекидано тешке него меко грешке. 2010 студија Rochester University је такође дала доказе да знатан део еморијских грешака је испрекидана тврда грешка.[10] Студије великог обима на не-ECC RAM у рачунарима и лаптоповима сугерише да неопажене меморијске грешке чине знатан део меморијских кварова: судија говори да је 1 у 1700 шанси за 1,5% тестиране меморије (екстраполацијом на приближено 26% шанси за целу меморију) да би рачунар имао меморијску грешке на 8 месеци.[11]

Паковање[уреди | уреди извор]

Из екеномских разлога, велике (главне) меморије које се налазе у личним рачунарима, радним станицама, и не-ручним играчким конзолама (као што су PlayStation и Xbox) обично се садрже динамички RAM (DRAM). Остали делови рачунара, као што су кеш меморије и бафер подаци на тврдим дисковима, обично користе статички RAM (SRAM).

Општи DRAM формати[уреди | уреди извор]

Динамичка меморија са случајним приступом се производи као интегрисано коло (IC) залепљено и монтирано у пластична паковања са металним пиновима за повезивање на контролне сигнале и магистрале. Рана коришћења појединачних DRAM IC су обично била или директно инсталирање на матичну плочу или на ISA картице за проширење; касније су били саствљени од више-чипног plug-in модула (DIMM, SIMM, итд.). Неке стандардне врсте модула су:

- DRAM чип (интегрисано коло или IC)

- Dual in-line Package (DIP)

- DRAM (меморијски) модули

- Single In-line Pin Package (SIPP)

- Single In-line Memory Module (SIMM)

- Dual In-line Memory Module (DIMM)

- Rambus In-line Memory Module (RIMM), технички је DIMM али се зове RIMM због слота.

- Small outline DIMM (SO-DIMM), око половине редовних DIMM-а, углавном се користе у notebook-овима, small footprint PCs (рачунар са релативно малим димензијама - као што је Mini-ITX матична плоча), надоградивим канцеларијским штампачима и мрежном хардверу попут рутера. Долазе у верзијама са:

- 72-pin (32-bit)

- 144-pin (64-bit) користи се за SDRAM

- 200-pin (72-bit) користи се за DDR SDRAM и DDR2 SDRAM

- 204-pin (64-bit) користи се за DDR3 SDRAM

- Small outline RIMM (SO-RIMM). Мања верзија RIMM-а, користе се у лаптоповима. Технички она је SO-DIMM али се зове SO-RIMM због свог слота.

- Наслагани у релацији са не-наслаганим RAM модулима

- Наслагани RAM модули садрже два или више RAM чипа наслаганих један на други. Ово омогућава да велики модули буду произведени коришћењем јефтинијег мање густине wafer-а (wafer: такође називан slice или substrate је танко парче полупроводничког материјала, као што је кристал силицијума, који се користи за израду интегрисаних кола и других микроуређаја). Наслагани чип модули користе више снаге, и имају тенденцију да раде топлије него не-наслагани модули. Наслагани модули могу бити направљени коришћењем старих TSOP или нових BGA стил IC чипова.

Уобичајени DRAM модули[уреди | уреди извор]

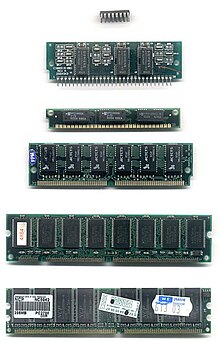

Уобичајени DRAM пакети илустровани десно, од врха до дна, су:

- DIP 16-pin (DRAM чип, обично pre-fast режим стране DRAM (FPRAM))

- SIPP 30-pin (обично FPRAM)

- SIMM 30-pin (обично FPRAM)

- SIMM 72-pin (често проширени подаци од DRAM (EDO DRAM) али FPRAM није упбичајен)

- DIMM 168-pin (SDRAM)

- DIMM 184-pin (DDR SDRAM)

- RIMM 184-pin (RDRAM) није приказан

- DIMM 240-pin (DDR2 SDRAM и DDR3 SDRAM) није приказан

Величина меморије DRAM модула[уреди | уреди извор]

Тачан број бајтова у једном DRAM модулу је увек интеграл снаге од двојке (степен двојке). 512 MB (као што је означено на модулу) SDRAM DIMM, заправо садржи 512 MiB (мебибајтова) = 512 × 220 бајтова = 229 бајтова = тачно 536.870.912 бајтова), а може бити састављен од 8 или 9 SDRAM чипова, од којих сваки садржи 512 Mib (мебибитова) капацитета, и сваки од њих доприноси 8 битова на DIMM-овој 64- или 72-битној ширини. За поређење, 2 GB SDRAM модул садржи 2 GiB (гигибајта) = 2 × 230 бајтова = 231 бајтова = тачно 2.147.483,648 бајта меморије. Модул обично има 8 SDRAM чипова од којих је сваки 256 MiB.

Верзије[уреди | уреди извор]

Док су основна DRAM ћелија и низ задржали исту основну структуру (и перформансе) током много година, било је много различитих интерфејса за комуникацију са DRAM чиповима. Када неко говори о "DRAM врстама“, то се генерално односи на интерфејс који се користи.

Асинхрони DRAM[уреди | уреди извор]

Асинхрони DRAM чип има везе напајања, неколико адресних улаза (обично 12), и неколико (обично један или четири) двосмерних линија података. Постоје четири ниско-активна контролна сигнала:

- /RAS, Row Address Strobe. Адресни улази су заробљени на силазној ивици /RAS-а, и изабере ред који треба да се отвори. Ред се одржава отвореним све док је /RAS низак

- /CAS, Column Address Strobe. Адресни улази су заробљени на силазној ивици /CAS-а, и избор колоне из тренутно отвореног реда да чита или пише.

- /WE, Write Enable. Овај сигнал одређује да ли је силазна ивица /CAS чита (ако је висока) или пише (ако је ниска). Ако је ниска, улазни подаци су такође заробљнени на силизаној ивици /CAS.

- /OE, Output Enable. То је додантни сигнал који контролише излаз на пиновима података У/И. Пинови података су вођени DRAM чипом ако су /RAS и /CAS ниски, /WE је висок, и /OE низак. У многим апликацијама, /OE може бити трајно повезан као низак (излаз је увек омогућен), али то може бити корисно када се повезује више меморијских чипова паралелно.

Овај интерфејс омогућава директну контролу интерног тајмингу. Када је /RAS низак, са /CAS цилкус не сме да се врше покушаји све док sense amplifiers не осети меморијско стање, и /RAS несме да буде враћен на високо све док се ћелије за складиштење не освеже. Када је /RAS високо, он мора бити задржан високо довољно дуго да се заврши претходно напајање.

Иако је RAM асинхрон, сигнали се обично генеришу помоћу меоријског контролера генератора такта, који ограничава њихово време множења циклуса генератора такта контролера.

RAS Only Refresh (ROR)[уреди | уреди извор]

Класични асинхрони DRAM се освежава отварањем сваког реда опет.

Циклус освежавања се дистрибуише током целог интервала освежење на такав начин да се сви редови освеже у траженом интервалу. При освежавању једног реда меморијског низа који користи /RAS Only Refresh, следећи кораци морају да се јаве:

- Адреса реда која треба да се освежи мора да се преда улазним адресним пиновима

- /RAS мора да се пребаци са високог на низак. /CAS мора остати висок.

- На крају потребне количине времена, /RAS мора да се врати на високо.

Омо може да се уради помоћу снабдевања реда адресе и пулсирањем /RAS-а ниско; за то није неопходно да се изврши било какав /CAS циклус. Екстерни бројач је потребан да опет врши итерацију кроз редове адреса.[12]

CAS пре RAS освежења (CBR)[уреди | уреди извор]

Због практичности, бројач је брзо уграђен у сам RAM чип. Ако је /CAS линија доведена ниско пре /RAS (обично у нелегалним раду), онда DRAM игнорише адресе улаза и користи унутрашњи бројач да изабере ред који да отвори. Ово је познато као /CAS-пре-/RAS (CBR) освежење. Претходно наелектрисање кола се искључује.

Ово је постао стандардни облик освежавања за асинхрони DRAM, и то је само један облик који се генерално користи са SDRAM-ом.

Скривено освежавање[уреди | уреди извор]

С обзиром на подршку CAS-пре-RAS освежења, могућ је да deassert (низак логички излаз) /RAS док држимо /CAS ниско да би се одржали излазни подаци. Ако се /RAS поново потврди, ово обавља CBR циклусе освежења док DRAM излази остају валидни. Пошто се излазни подаци не прекидају, ово је познато као „скривео освежавање“.[13]

Видео DRAM (VRAM)[уреди | уреди извор]

VRAM је dual-ported варијанта DRAM-а која је некада био најчешће коришћена за складиштење фрејм-бафера у неким графичким адаптерима.

Window DRAM (WRAM)[уреди | уреди извор]

WRAM је варијанта VRAM-а који се некада користио у графичким адаптерима као што су Matrox Millenium и ATI 3D Rage Pro. WRAM је дизаниран да ради боље и кошта мање него VRAM. WRAM нуди и до 25% већи пропусни опсег него VRAM и убрзање које обично користи графичке операције као што су текст цртање и блок попуне.[14]

Fast page mode DRAM (FPM DRAM)[уреди | уреди извор]

Fast page mode (брзи мод странице) DRAM-а се такође зове FPM DRAM, FPRAM, Page mode DRAM, Fast page mode memory, или Page mode memory.

У моду странице, ред DRAM-а може се држати „отвореним“ држањем /RAS ниским док извршава више читања или писања са одвојеним пулсевима /CAS-а тако да узастопна читања или писања у реду не трпе одлагање претходног напајања и приступа реду. Ово повећава перформансе система када рафално чита или пише податке.

Статичка колона је варијанта мода странице у којој адреса колоне не треба да се чува у, него, улазна адреса може да се промени са /CAS-ом задржаним ниско, а излаз података ће бити ажуриран у складу са неколико наносекунди касније.

Nibble mode је још једана варијанта у којој четири узастопне локације у овиру реда могу бити приступне са четири узастопна импулса /CAS-а. Разлика од нормалног режима странице је та да се адресни улази не користе за друге кроз четири /CAS ивице; они су генерисани интерно почев од адресе доношења првих /CAS ивица.

Extended data out DRAM (EDO DRAM)

EDO DRAM, понекад називају Hyper Page Mode омогућен DRAM, је сличан Fast Page Mode DRAM-у са додатним функцијама да нови приступ циклусу може бити покренут уз задржавање излаза података претходног активног циклуса. Првобитно произведен у Edo, Japan, EDO је бакроним који је сковао проналазач, млади Kunihiko Kodaira. Ова нова метода циклуса омогућава одређену количину преклапања у раду (проточна обрада), што омогућава нешто боље перформансе. Он је био 5% бржи од FPM DRAM-а, кога је почео замњивати 1995. године, када је Intel представио 430FX чипсет који подржава EDO DRAM.

Да будемо прецизни, EDO DRAM почиње излаз података на силазној ивици /CAS-а, али не спречава излаз када /CAS поново расте. Он одржава излаз важећим (тако продужава време излаза података) све док или /RAS deasserted, или нова /CAS силазна ивица изабере другу адресу колоне.

Једно-циклусни EDO има могућност да изврши комплетану меморијску трансакцију у једном циклусу генератора такта. Иначе, сваки секвенцијални приступ RAM-у у оквиру исте странице траје два циклуса генератора такта уместо три, када је једном већ изабрана страница. EDO перформансе и могућности дозвољавају да помало замени раније спори L2 кеш у PC. Он је створио прилику да се смањи огроман губитак перформанси са L2 кешом, чинећи системе јефтинијим при изградњи. Ово је такође добро за notebooks, због проблема са њиховим ограничењем form factor, и животом батерије. EDO са L2 кешом био је осетно бржи од старије FPM/L2 комбинације.

Једно-циклусни EDO DRAM постао је веома популаран за видео картице крајем 1990. година. Био је веома јефтин, а ипак скоро исто ефикасан за обављање као далеко скупљи VRAM.

Доста опреме које је узео 72-пински SIMM могли су да користе FPM или EDO. Проблеми су могући, посебно када се мешају FPM or EDO. Рани Hewlett-Packard штампачи су имали уграђен FPM RAM; неки, али не сви, модели су радили ако су додати додатни EDO SIMM-ови.[15]

Рафални EDO DRAM (BEDO DRAM)[уреди | уреди извор]

Еволуција EDO DRAM, Рафалног EDO DRAM, могла је да обради четири меморијске адресе у једном рафалу, за максимум од 5-1-1-1, који чува додатна три циклуса преко оптималног дизајна EDO меморије. То је учињено додавањем бројача адресе на чипу да прати траг следеће адресе. BEDO је такође додао стање проточне обраде омогућавајући да се циклус приступа страници подели у две компоненте. Током операције меморијског читања, прва компонента приступа подацима из меморијског низа на излазном стању (други леч). Друга компонента доводи магистралу података са овог леча на одговарајући логички ниво. Пошто су подаци већ у излазном баферу, постиже се брже време приступа (и до 50% за велике блокове података) него са традиционалним EDO-м.

Иако је BEDO DRAM показао додатну оптимизацију на EDO, временом он је био доступан на тржишту где је направио је значајну инвестицију према синхроном DRAM-у или SDRAM-у [1][мртва веза]. Иако је BEDO RAM био супериорнији у односу на SDRAM на неки начин, каснија технологија брзо избацила BEDO.

Multibank DRAM (MDRAM)[уреди | уреди извор]

Multibank DRAM примењује технику преплитања за главну меморију до кеш меморије нива два да обезбеди јефтинију и бржу алтернативу за SRAM. Чип дели своје меморијске капацитете у мале блокове од 256 kB и омогућава рад на две различите банке у једном циклусу.

Ова меморија се првенствено користила у графичким картицама са Tseng Labs ET6x00 чипсетом, направљена од MoSys. Плоче засноване на овом чипсету често су користиле необичну конфигурацију величине RAM-а од 2.25 MB, захваљујући способности MDRAM-а да лакше буде имплементиран у различитим величинама. Ова величина од 2.25 MB омогућава 24-битну боју на резолуцији од 1024х768, веома популарна поставка екрана у време картица.

Синхрони графички RAM (SGRAM)[уреди | уреди извор]

SGRAM је специјализована форма SDRAM за графичке адаптере. Она додаје функције као што су бит маскирање (писање на одређеној бит равни без утицаја на другу) и блок писање (пуњење блока меорије са једном бојом). За разлику од VRAM и WRAM, SGRAM је single-ported. Међутим, он може да отвори две странице истовремено, што симулира dual-port природу других VRAM модула.

Синхрони динамички RAM (SDRAM)[уреди | уреди извор]

SDRAM значајно ревидира асинхрони меморијски интерфејс, додајући генераторску такт (и генераторски такт омогућава) линију. Сви остали сигнали се примају на узлазну ивицу генераторског такта.

/RAS и /CAS улази више не делују дуже као фарови, али су уместо тога, заједно са /WE, део 3-битне команде:

| /CS | /RAS | /CAS | /WE | Адреса | Команда |

|---|---|---|---|---|---|

| H | x | x | x | x | Инхибиција команде (нема операција) |

| L | H | H | H | x | Нема операција |

| L | H | H | L | x | Рафални прекид: зауставити рафално читање или писање у току |

| L | H | L | H | колона | Читати са тренутно активног реда |

| L | H | L | L | колона | Писати у тренутно активни ред |

| L | L | H | H | ред | Активирати ред за читање и писање |

| L | L | H | L | x | Претходно напуњен (деактивирари) тренутни ред |

| L | L | L | H | x | Аутоматско освежавање: Освежити један ред сваке банке, коришћењем унутрашњег бројача |

| L | L | L | L | режим | Учитавање више регистара: Адресна магистрала спецификује DRAM операције мода |

/OE линијска функције је проширена по бајту на "DQM" сигналу, који контролише улаз података (писања) поред излаза за податке (читање). Ово омогућава DRAM чипу да буде шири од 8 битова, док још увек подржава писање бајт-гранулације.

Многи временски параметри су остали под контролом DRAM контролера. На пример, минимално време мора проћи између активирања реда и команде читања или писања. Један важан параметар мора бити програмиран у самом SDRAM чипу, а то је CAS кашњење. То је број циклуса генератора такта дозвољених за унутрашње операције између команде читања и прве речи податка која се јавља на магистрали података. Команда "Load mode register" се користи да пренесе ову вредност SDRAM чипу. Остали параметри су подесиве дужине рафалног читања и писања, односно броја речи пренетих по команди писања или читања.

Најзначајнија промена, главни разлог зашто је SDRAM заменио асинхрони RAM, је подршка за више унутрашњих банака унутар DRAM чипа. Користећи неколико битова „банчине адресе“ која прати сваку команду, друга банка може да се активира и започне читање података док је читање прве банке још увек у току. Помоћу наизменичних банака, SDRAM уређај може да задржи магистралне податке стално заузетим, на начин који асинхрони DRAM не могу.

Једнострука брзина преноса (SDR)[уреди | уреди извор]

Једнострука брзина преноса SDRAM (понекад познат као SDR) је асинхрони облик DRAM-а.

Двострука брзина преноса (DDR)[уреди | уреди извор]

Двострука брзина преноса SDRAM ('DDR) је касније развијена од SDRAM, користила се у PC меморији почетком 2000. години. Накнадне верзије су нумерисане секвенцијално (DDR2, DDR3, итд.). DDR SDRAM интерно обавља дуплу ширину приступа у генераторском такту, и користи двоструке брзине преноса интерфејса да пренесе половину на сваку ивицу генераторског такта. DDR2 и DDR3 су повећали овај фактор на 4х и 8х, респективно испоручујућу рафално 4-речи и 8-речи током 2 и 4 циклуса генераторског такта, респективно. Интерна брзина приступа је углавном непромењена (200 милиона у секунди за DDR-400, DDR2-800 и DDR3-1600 меморије), али сваки приступ преноси више података.

Директан рамбус DRAM (DRDRAM)[уреди | уреди извор]

Директан рамбус DRAM (DRDRAM) је развио Рамбус.

Pseudostatic RAM (PSRAM)[уреди | уреди извор]

PSRAM или PSDRAM је димични RAM са уграђеним освежавањем и колом контроле адресе да би се слично понашали као статички RAM (SRAM). Он комбинује високу густину DRAM-а са лакоћом коришћења истинског SRAM-а. PSRAM (направљен од стране Numonyx) се користи у Apple iPhone и другим уграђеним системима као XFlar Platform.[16]

Неке DRAM компоненте имају „само-освежавајући-режим“. Иако то подразумева много исте логике која је потребна за псеудо-статичке операције, овај режим је често еквивалентан са режимом мировања. Предвиђен је пре свега да омогући систему да суспендује операције свог DRAM контролера ради уштеде енергије без губитка податак сачуваних у DRAM-у, и да не дозволити операције без одвојеног DRAM контролера као што је случај са PSRAM-ом.

Уграђена варијанта PSRAM се продаје од MoSys под именом 1T-SRAM. То је технички DRAM, али се понаша више као SRAM. Користи се у Nintendo Gamecube и Wii конзоли.

Смањено кашњење DRAM (RLDRAM)[уреди | уреди извор]

Смањено кашњење DRAM-а је висока перформанса двоструке брзине преноса (DDR) SDRAM који комбинује брзи, случајни приступ са високим пропусним опсегом, углавном намењен умрежавању и кеширању апликација

1T DRAM[уреди | уреди извор]

За разлику од свих осталих варијанти описаних у овом одељку овог чланка, 1T DRAM је другачији начин изградње основне DRAM бит ћелије. 1T DRAM је „капацитаторска“ бит ћелија дизајнирана да складишти податке у паразитском телу кондензатора који је сатавни део силикона, на изоловани (SOI) транзистор. Посматрање сметње у логичком дизајну, овај ефекат плутајућег тела може се користити за складиштење података. Иако је још потребно освежавање, чита се без разарања; напуњена складишта изазивају мерљив помак у напону прага транзисотра.[17]

Постоји неколико типова 1T DRAM драм меморије: комерцијализован Z-RAM од Innovative Silicon, TTRAM од Renesas и A-RAM од UGR/CNRS конзорцијума.

Класична један-транзистор/један-капацитатор (1T/1C) DRAM ћелија се такође понекад назива као "1T DRAM", нарочито у поређењу 3T и 4T DRAM који је замењен 1970. године.

Сигурност[уреди | уреди извор]

Иако динамичка меморија је дефинисана и гарантује да чува свој садржај када се снабдева са напајањем и када се освежава у кратким временским интервалима (најчешће 64 ms), меморијска ћелија кондензатора често задржава своју вредност знатно дуже, посебно на ниским температурама. Под неким условима већина података на DRAM-у може бити враћена чак ако он није био освеживан неколико минута.[18]

Ово својство може да се користи да се заобиђе безбедност и опораве подаци ускладиштени у меморији и претпостаља се да је уништен у нестајању струје брзим рестартовањем рачунара и дамповањем садржаја RAM-а, или хлађењем чипа и њиховим пребацивањем на други рачунар. Такав напад је демонстрирао заобилажење популарне енкрипције диск система, као што је отворени код TrueCrypt, Microsoft's BitLocker Drive Encryption, и Еплов FileVault.[тражи се извор] Ова врста напада на рачунар се често назива хладно покретање напада.

Види још[уреди | уреди извор]

Референце[уреди | уреди извор]

- ^ Copeland 2006, стр. 301

- ^ Spec Sheet for Toshiba "TOSCAL" BC-1411

- ^ Toshiba "Toscal" BC-1411 Desktop Calculator (The introduction date is listed here as November 1965, but this is a year too early and appears to be a typographical error.)

- ^ „Micron 4 Meg x 4 EDO DRAM data sheet” (PDF). Архивирано из оригинала (PDF) 27. 09. 2007. г. Приступљено 19. 12. 2013.

- ^ cmx1024-3200.ai

- ^ https://web.archive.org/web/20040529091249/http://www.corsairmemory.com/corsair/products/specs/twinx1024-3200xl.pdf

- ^ а б Borucki, "Comparison of Accelerated DRAM Soft Error Rates Measured at Component and System Level", 46th Annual International Reliability Physics Symposium, Phoenix, (2008). стр. 482–487

- ^ http://www.cs.toronto.edu/~bianca/papers/sigmetrics09.pdf

- ^ „A Memory Soft Error Measurement on Production Systems[[Категорија:Ботовски наслови]]”. Архивирано из оригинала 14. 02. 2017. г. Приступљено 19. 12. 2013. Сукоб URL—викивеза (помоћ)

- ^ Li, Huang; Shen, Chu (2010). „"A Realistic Evaluation of Memory Hardware Errors and Software System Susceptibility". Usenix Annual Tech Conference 2010” (PDF).

- ^ „Cycles, cells and platters: an empirical analysis of hardware failures on a million consumer PCs. Proceedings of the sixth conference on Computer systems (EuroSys '11).” (PDF). 2011. стр. 343—356.

- ^ „Архивирана копија” (PDF). Архивирано из оригинала (PDF) 29. 08. 2017. г. Приступљено 19. 12. 2013.

- ^ Various Methods of DRAM Refresh Архивирано на сајту Wayback Machine (3. октобар 2011) Micron Technical Note TN-04-30

- ^ The PC Guide, definition of WRAM.

- ^ Page on memory upgrades for HP printers

- ^ „EE Times teardown of iPhone 3G”. Архивирано из оригинала 22. 01. 2013. г. Приступљено 19. 12. 2013.

- ^ Sallese, Jean-Michel (20. 6. 2002). „Principles of the 1T Dynamic Access Memory Concept on SOI” (PDF). MOS Modeling and Parameter Extraction Group Meeting. Wroclaw, Poland. Архивирано из оригинала (PDF) 22. 3. 2003. г. Приступљено 7. 10. 2007.

- ^ Scheick, Leif Z.; Guertin, Steven M.; Swift, Gary M. (2000). „Analysis of radiation effects on individual DRAM cells”. IEEE Trans. on Nuclear Science. 47 (6): 2534—2538. ISSN 0018-9499. doi:10.1109/23.903804. Приступљено 8. 8. 2013.

Литература[уреди | уреди извор]

- Copeland, Jack B. (2006). Colossus: The Secrets of Bletchley Park's Codebreaking Computers. Oxford: Oxford University Press. стр. 301.