Magistrala sa prednje strane

Magistrala sa prednje strane (engl. Front-side bus, FSB)) je bila interfejs za kompjutersku komunikaciju (magistrala). Ovaj interfejs se često koristio u kompjuterima baziranim na Intel-ovim čipovima tokom 90-ih godina 20. veka i prvih godina 21. veka. EV6 magistrala, koja joj je bila konkurencija, je vršila istu funkciju kod AMD-ovih procesora. Obe magistrale obično prenose podatke između procesora (CPU) i središta za kontrolu memorije, poznatijeg kao Severni most.[1]

U zavisnosti od implementacije, neki kompjuteri su takođe mogli da imaju magistralu sa zadnje strane koja povezuje procesor sa kešom. Ova magistrala i keš koji je povezan sa njom su brži nego da se pristupa sistemskoj memoriji (ili RAM) preko magistrale sa prednje strane. Brzina magistrale sa prednje strane se obično koristi kao važno merilo performansi kompjutera.

Originalna arhitektura magistrale sa prednje strane je bila zamenjena sa HyperTransport, Intel QuickPath Interconnect ili Direct Media Interface kod modernih procesora.

Istorija[uredi | uredi izvor]

Ovaj termin je počeo da koristi Intel u vreme kada su Pentium Pro i Pentium II bili najavljeni 90-ih godina 20. veka.

"Prednja strana" se odnosi na eksterni interfejs od procesora do ostatka kompjuterskog sistema, za razliku od zadnje strane, gde se magistrala sa zadnje strane povezuje na keš (i potencijalno sa ostalim procesorima).[2]

FSB se najčešće koristi na matičnim pločama vezanim za PC (uključujući i servere), a ređe kod magistrala za podatke i adrese kod ugrađenih sistema i sličnih manjih kompjutera. Ovaj dizajn je predstavljao poboljšanje performanse u ondosu na dizajn sa jednom sistemskom magistralom koja se koristila prethodnih decenija.

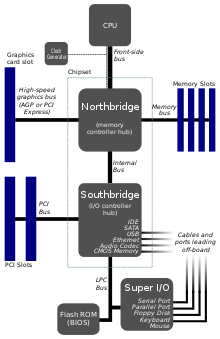

Magistrale sa prednje strane obično povezuju procesor sa ostatkom hardvera preko čipseta. Ovaj čipset je Intel implementirao kao severni most i južni most. Ostale magistrale kao PCI, AGP i memorijske magistrale se povezuju na čipset kako bi podaci proticali između povezanih uređaja. Ove sekundarne sistemske magistrale obično imaju brzinu koja zavisi od frekvencije magistrale sa prednje strane, ali nisu obavezno i sinhronizovane sa njom.

Kao odgovor na AMD-ovu Torrenza inicijativu, Intel je otvorio svoj FSB CPU soket uređajima drugih proizvođača.[3] Pre ove najave, koju je Intel obznanio u leto 2007. godine na Intel Developer Forum-u u Pekingu, Intel je strogo pazio ko ima pristup FSB-u, dozvoljavajući samo Intel-ove procesore u CPU soket. Prvi primer je bio FPGA ko-procesor, rezultat saradnje Intel-Xilinx-Nallatech[4] i Intel-Altera-XtremeData (isporučivan od 2008. gofine).[5][6][7]

Povezane brzine komponenti[uredi | uredi izvor]

Procesor[uredi | uredi izvor]

Frekvencija na kojoj procesor (CPU) radi se određuje tako što se na brzinu magistrale sa prednje strane primeni umnožilac takta. Na primer procesor koji radi na 3200 MHz može da koristi 400 MHz FSB. Ovo znači da postoji interno podešavanje umnožioca takta (poznatko kao odnos magistrala/jezgro) koje iznosi 8, to jest, CPU je podešen da radi na 8 puta većoj frekvenciji od magistrale sa prednje strane: 400 MHz × 8 = 3200 MHz. Različite brzine CPU-a se dobijaju tako što se menja bilo frekvencija FSB-a bilo CPU umnožilac.

Memorija[uredi | uredi izvor]

Podešavanje brzine FSB-a je direktno povezano sa kvalitetom brzine memorije koju sistem mora da koristi. Memorijska magistrala povezuje severni most i RAM, isto kao što i magistrala sa prednje strane povezuje procesor i severni most. Ove dve magistrale često moraju da rade na istoj frekvenciji. Povećavajući frekvenciju magistrale sa prednje strane na 450 MHz u najvećem broju slučaja znači da memorijska magistrala raditi na 450 MHz.

U novijim sistemima može da se vidi memorijski odnos od "4:5" i slično. Memorija će biti 5/4 puta brža od FSB-a u ovoji situaciji, što znači da će magistrala od 400 MHz raditi sa memorijom od 500 MHz. Ovo se obično naziva 'asinhroni' sistem. Zbog razlike u procesorskoj i sistemskoj arhitekturi, sistemske performanse mogu da variraju na neočekivane načine sa različitim FSB-memorija-odnosima.

Kod sinteze slike, zvuka, videa, video-igara, FPGA i kod naučnih aplikacija koje vrše malu količinu rada na svaki element većeg skupa podataka, FSB brzina postaje glavni problem po pitanju performanse. Spor FSB će naterati CPU da troši značajnu količinu vremena čekajući da podaci stignu od RAM-a. Međutim, ako su računske operacije za svaki element kompleksnije, procesor će duže vremena da ih izvršava; time će FSB biti u taktu jer je brzina pristupa memoriji smanjena.

Periferne magistrale[uredi | uredi izvor]

Slično memorijskoj magistrali, PCI i AGP magistrale takođe mogu da rade asinhrono u odnosu na magistralu sa prednje strane. U starijim sistemima, ove magistrale su funkcionisale na određenoj frakciji brzine magistrale sa prednje strane. Ovu frakciju je određivao BIOS. U novijim sistemima PCI, AGP, i PCI E periferne magistrale često dobijaju svoj taktni signal, što eliminiše njihovu zavisnost od tajminga magistrale sa prednje strane.

Overkloking[uredi | uredi izvor]

Overkloking je praksa primoravanja kompjuterskih komponenti da rade bolje nego što njihove normalne performanse dozvoljavaju, tako što se manipuliše frekvencija na kojoji je komponenta podešena da radi, i po potrebi, menja voltaža koja se šalje komponenti kako bi stabilnije funkcionisala na ovim većim frekvencijama.

Puno matičnih ploča dozvoljava korisniku da ručno podešava umnožilac takta i FSB podešavanja tako što menja skakače ili BIOS podešavanja. Skoro svi CPU proizvođači sada "zaključaju" prethodno podešeno podešavanje umnožioca u čip. Moguće je otključati neke zaključane procesore; na primer, neki AMD Athlon mogu biti otključani povezivanjem električnih kontakata preko tačaka na površini procesora. Neki drugi procesori od AMD-a i Intel-a su otključani od strane fabrike i korisnici i trgovci ih zbog ove karakteristike obeležavaju kao procesore "za entuzijaste". Povećavanjem FSB brzine može da se poveća brzina procesiranja jer se smanjuje kašnjenje izmeću CPU-a i severnog mosta.

Ova praksa tera komponente da rade brže nego što je predviđeno i može izazvati nepravilno ponašanje, pregrejavanje ili prevremeni kvar. Čak i ako kompjuteri izgledjau kao da rade normalno, problemi mogu da se pojave pri teškom opterećenju. Većina kompjutera kupljena od trgovaca ili proizvođača, kao što je Hjulet-Pakard ili Del, ne dozvoljavaju korisniku da menja umnožilac ili FSB podešavanja zbog verovatnoće nepravilnog ponašanja ili kvara. Matične ploče koje su kupljene odvojeno kako bi se napravila lična mašina češće dozvonjavaju korisniku da menja umnožilac i FSB podešavanja u BIOS-u.

Evolucija[uredi | uredi izvor]

Magistrala sa prednje strane je imala prednost veće fleksibilnosti i niže cene kada je prvi put bila dizajnirana. Jednostavni simetrični multiprocesori stavljaju nekoliko procesora na zajednički FSB, ali performanse se nisu linearno povećavale zbog uskog grla u protoku.

Magistrala sa prednje strane je korišćena u svim Intel Atom, Celeron, Pentium, Core 2, i Xeon procesorskim modelima do oko 2008. godine. Originalno, ova magistrala je bila centralna tačka povezivanja za sve sistemske uređaje i CPU.

Potencijal bržeg CPU-a je uzaludan ako ne može da donese instrukcije i podatke istom brzinom kojom ih i izvršava. CPU može biti dugo vreme neaktivan dok čeka da čita ili piše u glavnu memoriju, i zbog toga procesori visoke performanse zahtevaju visok protok i nisko kašnjenje pristupa memoriji. AMD je kritikovao magistralu sa prednje strane jer je bila stara i spora tehnologija koja ograničava sistemske performanse.[8]

Modernije vrste dizajna koriste point-to-point konekcije kao što su AMD-ov HyperTransport i Intel-ov DMI 2.0 ili QuickPath Interconnect (QPI). Ove implementacije uklanjaju tradicionalni severni most u korist direktne veze od CPU-a do Platform Controller Hub, južnog mosta ili I/O kontrolera.[9]

U tradicionalnoji arhitekturi, magistrala sa prednje strane je služila kao neposredna veza podataka između CPU-a i svih drugih uređaja u sistemu uključujući i glavnu memoriju. U sistemima baziranim na HyperTransport i QPI, sistemskoj memoriji se pristupa preko memorijskog kontrolera integrisanog u CPU, ostavljajući drugima da koriste protok na HyperTransport ili QPI vezi. Ovo povećava kompleksnost CPU dizajna ali dozvoljava veći protok kao i bolje skaliranje u multiprocesorskim sistemima.

Brzina prenosa[uredi | uredi izvor]

Maksimalni teoretski protok magistrale sa prednje strane je određen proizvodom širine putanje podataka, frekvencije (taktovi po sekundi) i broja prenosa podataka po taktnom ciklusu. Na primer, 64-bit (8-byte) široka FSB koja radi na frekvenciji od 100 MHz i izvršava 4 transfera po ciklusu, ima protok od 3200 megabajta po sekundi (MB/s):

- 8 B × 100 MHz × 4/cycle = 3200 MB/s

Broj prenosa po ciklusu takta zavisi od tehnologije koja se koristi. Na primer, GTL+ ima 1 prenos/ciklus, EV6 2 prenos/ciklus, i AGTL+ 4 prenos/ciklus. Intel naziva tehniku četiri prenosa po ciklusu Quad Pumping.

Veliki broj proizvođača pišu frekvenciju magistrale sa prednje strane u MHz, ali marketinški materijal obično navodi teoretsku efektivnu stopu signalizacije (koja se obično naziva megatransfer po sekundi ili MT/s). Na primer, ako matična ploča (ili procesor) ima magistralu podešenu na 200 MHz i vrši 4 prenosa po taktnom ciklusu, FSB se ocenjuje sa 800 MT/s. Protok magistrale sa prednje strane određuje broj prenosa svakog taktnog ciklusa, frekvencije, i broja bitova u svakom prenošenju.

Specifikacije nekoliko generacija popularnih procesora se nalaze u donjim tabelama.

Intelovi procesori[uredi | uredi izvor]

| Procesor | FSB frekvencija (MHz) | Prenosa/Ciklusu | Širina magistrale |

Brzina prenosa (MB/sec) |

|---|---|---|---|---|

| Pentium | 50 - 66 | 1 | 64-bit | 400 - 528 |

| Pentium Overdrive | 25 - 66 | 1 | 64-bit | 200 - 528 |

| Pentium Pro | 60 / 66 | 1 | 64-bit | 480 - 528 |

| Pentium MMX | 60 / 66 | 1 | 64-bit | 480 - 528 |

| Pentium MMX Overdrive | 50 / 60 / 66 | 1 | 64-bit | 400 - 528 |

| Pentium II | 66 / 100 | 1 | 64-bit | 528 / 800 |

| Pentium II Xeon | 100 | 1 | 64-bit | 800 |

| Pentium II Overdrive | 60 / 66 | 1 | 64-bit | 480 - 528 |

| Pentium III | 100 / 133 | 1 | 64-bit | 800 / 1064 |

| Pentium III Xeon | 100 / 133 | 1 | 64-bit | 800 / 1064 |

| Pentium III-M | 100 / 133 | 1 | 64-bit | 800 / 1064 |

| Pentium 4 | 100 / 133 | 4 | 64-bit | 3200 - 4256 |

| Pentium 4-M | 100 | 4 | 64-bit | 3200 |

| Pentium 4 HT | 133 / 200 | 4 | 64-bit | 4256 / 6400 |

| Pentium 4 HT Extreme Edition | 200 / 266 | 4 | 64-bit | 6400 / 8512 |

| Pentium D | 133 / 200 | 4 | 64-bit | 4256 - 6400 |

| Pentium Extreme Edition | 200 / 266 | 4 | 64-bit | 6400 / 8512 |

| Pentium M | 100 / 133 | 4 | 64-bit | 3200 / 4256 |

| Pentium Dual-Core | 200 / 266 | 4 | 64-bit | 6400 / 8512 |

| Pentium Dual-Core Mobile | 133 - 200 | 4 | 64-bit | 6400 - 8512 |

| Celeron | 66 - 200 | 1-4 | 64-bit | 528 - 6400 |

| Celeron Mobile | 133 - 200 | 1-4 | 64-bit | 4256 - 6400 |

| Celeron D | 133 | 4 | 64-bit | 4256 |

| Celeron M | 66 - 200 | 1-4 | 64-bit | 528 - 6400 |

| Celeron Dual-Core | 200 | 4 | 64-bit | 6400 |

| Celeron Dual-Core Mobile | 133 - 200 | 4 | 64-bit | 4256 - 6400 |

| Itanium | 100 / 133 | 1 | 64-bit | 800 / 1064 |

| Itanium 2 | 100 - 166 | 4 | 64-bit | 3200 - 5312 |

| Xeon | 100 - 400 | 4 | 64-bit | 3200 - 12800 |

| Core Solo | 133 / 166 | 4 | 64-bit | 4256 / 5312 |

| Core Duo | 133 / 166 | 4 | 64-bit | 4256 / 5312 |

| Core 2 Solo | 133 - 200 | 4 | 64-bit | 4256 - 6400 |

| Core 2 Duo | 200 - 333 | 4 | 64-bit | 6400 - 10656 |

| Core 2 Duo Mobile | 133 - 266 | 4 | 64-bit | 4256 - 8512 |

| Core 2 Quad | 266 / 333 | 4 | 64-bit | 8512 / 10656 |

| Core 2 Quad Mobile | 266 | 4 | 64-bit | 8512 |

| Core 2 Extreme | 266 - 400 | 4 | 64-bit | 8512 - 12800 |

| Core 2 Extreme Mobile | 200 / 266 | 4 | 64-bit | 6400 / 8512 |

| Atom | 100 - 166 | 4 | 64-bit | 3200 - 5312 |

AMD processors[uredi | uredi izvor]

| Procesor | FSB frekvencija (MHz) | Prenosa/Ciklusu | Širina magistrale | Brzina prenosa (MB/sec) |

|---|---|---|---|---|

| K5 | 50 - 66 | 1 | 64-bit | 400 - 528 |

| K6 | 66 | 1 | 64-bit | 528 |

| K6-II | 66 - 100 | 1 | 64-bit | 528 - 800 |

| K6-III | 66 / 100 | 1 | 64-bit | 528 - 800 |

| Athlon | 100 / 133 | 2 | 64-bit | 1600 - 2128 |

| Athlon XP | 100 / 133 / 166 / 200 | 2 | 64-bit | 1600 - 3200 |

| Athlon MP | 100 / 133 | 2 | 64-bit | 1600 - 2128 |

| Mobile Athlon 4 | 100 | 2 | 64-bit | 1600 |

| Athlon XP-M | 100 / 133 | 2 | 64-bit | 1600 - 2128 |

| Duron | 100 / 133 | 2 | 64-bit | 1600 - 2128 |

| Sempron | 166 / 200 | 2 | 64-bit | 2656 - 3200 |

Reference[uredi | uredi izvor]

- ^ Scott Mueller (2003). Upgrading and repairing PCs (15th izd.). Que Publishing. str. 314. ISBN 978-0-7897-2974-3.

- ^ Todd Langley and Rob Kowalczyk (januar 2009). „Introduction to Intel Architecture: The Basics” (PDF). "White paper". Intel Corporation. Arhivirano iz originala (PDF) 7. 6. 2011. g. Pristupljeno 28. 5. 2011.

- ^ Charlie Demerjian (17. 4. 2007). „Intel opens up its front side bus to the world+dog: IDF Spring 007 Xilinx heralds the bombshell”. The Inquirer. Arhivirano iz originala 07. 10. 2012. g. Pristupljeno 28. 5. 2011.

- ^ „Nallatech™ Launches Early Access Program for the Industry’s First FSB-FPGA Module”. Business Wire news release. Nallatech. 18. 9. 2007. Pristupljeno 14. 6. 2011.

- ^ „XtremeData Offers Stratix III FPGA-Based Intel FSB Module”. Business Wire news release. Chip Design magazine. 18. 9. 2007. Arhivirano iz originala 23. 07. 2011. g. Pristupljeno 14. 6. 2011.

- ^ Ashlee Vance (17. 4. 2007). „High fiber diet gives Intel 'regularity' needed to beat AMD”. The Register. Pristupljeno 28. 5. 2011.

- ^ „XtremeData Begins Shipping 1066 MHz Altera Stratix III FPGA-Based Intel FSB Module”. Business Wire news release. XtremeData. 17. 6. 2008. Pristupljeno 14. 6. 2011.

- ^ Allan McNaughton (29. 9. 2003). „AMD HyperTransport Bus: Transport Your Application to Hyper Performance”. AMD. Arhivirano iz originala 25. 3. 2012. g. Pristupljeno 15. 6. 2016.

- ^ „An Introduction to the Intel QuickPath Interconnect” (PDF). Intel Corporation. 30. 1. 2009. Pristupljeno 14. 6. 2011.